[URS] Gradivo

verratti

Daho_Cro

1.

void conf (int c){

if(c == 0){

while(1);

}else if(c == 1){

volatile uint32_t tmp;

RCC -> AHB1ENR |= (0x1UL << 1); // omoguciti takt za GPIOB

tmp = RCC -> AHB1ENR; // dummy read potreban nakon omogucavanja takta

GPIOB -> MODER &= 0x11110000UL; // ocistiti vrijednosti 0-7 prikljucaka

GPIOB -> MODER |= 0x00000000UL; // postaviti 0-7 kao ulazne, vjv moze i bez ove linije

}else if(c == 2){

volatile uint32_t tmp;

RCC -> AHB1ENR |= (0x1UL << 1); // omoguciti takt za GPIOB

tmp = RCC -> AHB1ENR; // dummy read potreban nakon omogucavanja takta

GPIOB -> MODER &= 0xFFFF0000UL; // ocistiti vrijednosti 0-7 prikljucaka

GPIOB -> MODER |= 0x00005555UL; // postavi prikljucke 0-7 kao izlazne

GPIOB -> OTYPER &= 0xFF00UL; // postavi prikljucke 0-7 tako da imaju 2 logicka stanja (pola)

GPIOB -> OSPEEDR |= 0xFFFFUL; // i postavi da se mogu mijenjati najvecom mogucom brzinom

}else{

volatile uint32_t tmp;

RCC -> AHB1ENR |= (0x1UL << 1); // omoguciti takt za GPIOB

tmp = RCC -> AHB1ENR; // dummy read potreban nakon omogucavanja takta

GPIOB -> MODER &= 0xFF00FFFFUL; // ocisti prikljucke 8-11

GPIOB -> MODER |= 0x00550000UL; // postavi 8-11 kao izlazne

GPIOB -> OTYPER |= 0x0F00UL; // postavi ih sa otvorenim odvodom

GPIOB -> PUPDR |= 0x00550000UL; // postavi ih sa priteznim otpornikom prema napajanju (pull-up)

}

}Bobinator

Rom Jova (Željezo/bakar) GPIOB -> MODER &= 0×11110000UL; // ocistiti vrijednosti 0-7 prikljucaka

da tu ne ide mozda 0xFFFF0000UL; ? jer ovako postavljamo ostale kao general purpose, a vj ih treba ostavit kako jesu

verratti

Daho_Cro

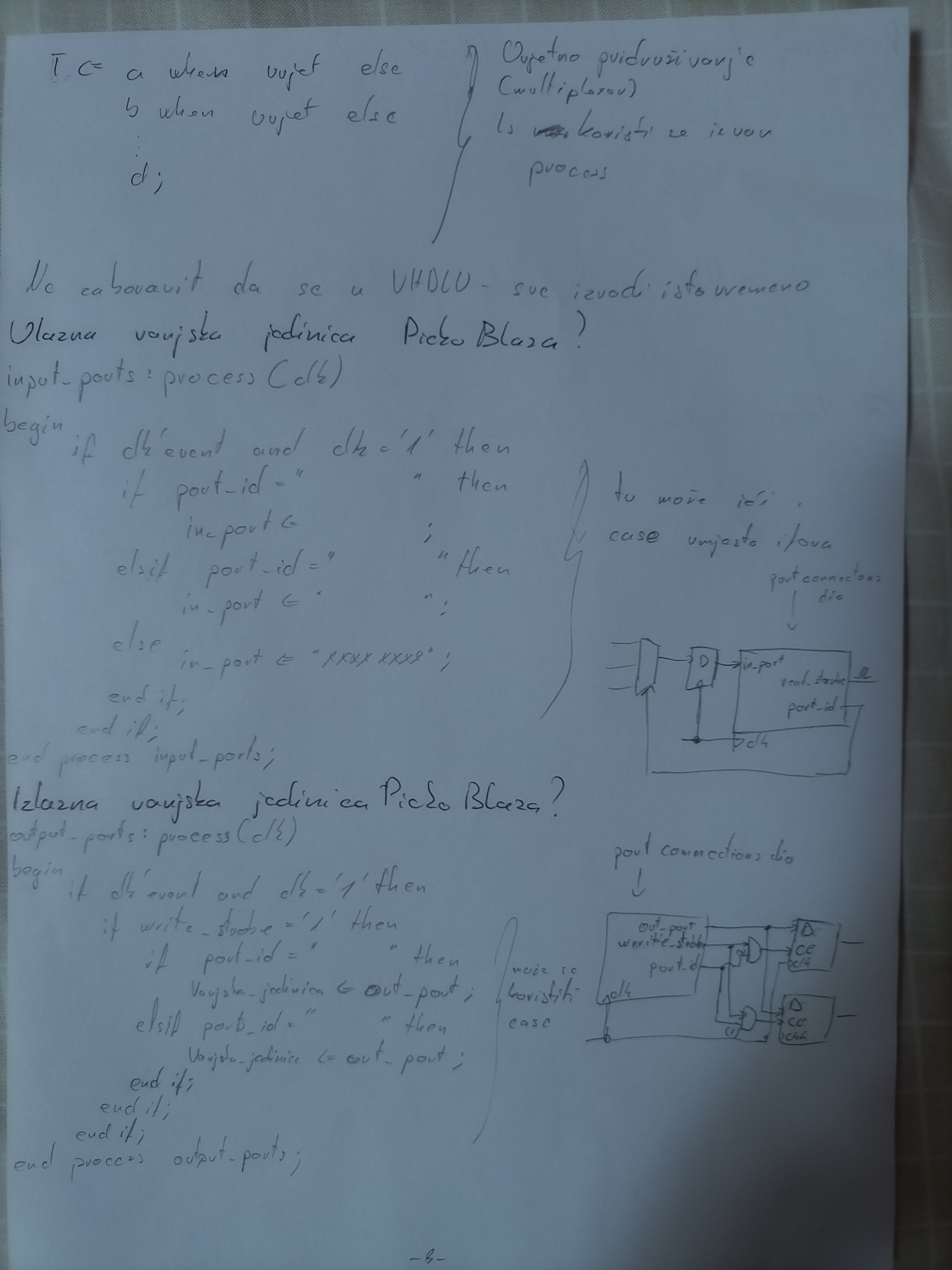

3.

void init_SysTick(void){

// odrediti prioritet sistemskog prekida

SCB -> SHP[11] = (0x2UL << 4); // prioritet se nalazi u gornjem niblu bajta, zato ide << 4

// grupiranje prekida tj podesavanje

SCB -> AIRCR = SCB -> ( (AIRCR & 0xF8FFUL) | 0x05FA0000UL );

// inicijalizacija sistemskog brojila

SysTick -> VAL = 0x0UL; // trenutna vrijednost 0

SysTick -> LOAD = 0x5207UL; // AHB = 168MHz, 168/8 = 21MHz... (21*10^6)/(1*10^3) = 21000 tj. 20999 u dekadskom, sto je 5207 hex

SysTick -> CTRL |= 0x3UL; // za omoguciti brojilo, prekid i odabrati izvor takta

}

// prekidna funkcija

void __atribute_((interrupt)) SysTickHandler(void){

volatile uint32_t V1,V2;

int brojac = 0;

++V1;

++brojac;

if(brojac == 10){

++V2;

brojac = 0;

}

}Trava

Rom Jova (Željezo/bakar) Mislim da je sve dobro, osimi inicalizacije brojača u interrupt-u. Svaki put kad pozoveš interrupt brojac ode u 0, pa ti nikad neće doći do 10.

verratti

Molio bi nekog da provjeri ovo sta sam pisao jel to uopce ok i ako netko moze rijesiti 2. zadatak, ne shvacam bas sta bi trebalo raditi…..

Andrej1901

- Zadatak RC oscilator sa Schmittovim okidnim sklopom

Shema je u materijalima sa predavanja stranica 67.

Opis rada: izvode se pomoću Schmitt trigger invertora s otpornikom u povratnoj vezi i kondenzatorom prema masi.

Na početku je kondenzator prazan i daje Uc=0V na ulaz invertora koji daje 1 na izlazu i tako se kondenzator puni preko otpornika u povratnoj vezi po ekponencijali, kad naraste do gornje granice onda inverter daje 0 na izlazu pase kondenzator prazni po eksponencijali, te kada taj napon Uc padne na donju granicu taj se postupak ponavlja. Kad inverter daje 1 vrijednost tog napona je označena na grafu kao Ugornje, kad daje 0 to je vrijednost Udonje.

Ovaj oscilator je jako pouzdan i odma starta ali niej točan bas i nije stabilan za neka precizna mjerenja itd.

Ja mislim da ako je dao ovdje Schmittov oscilator da bi na ispitu mogao biti kvarcni, pa cu i njega napisat i objavit

Toni007

ako bi netko znao riješiti ovaj zadatak, i postati tu jer je bio apsolutno svake godine na ZI, pa pretpostavljam i očekujem neku varijaciju i na našem

ja ga baš i ne znam riješiti, pa bi bilo od velike pomoći i meni i kolegama, ako bi netko uspio riješiti ovo i sherati

Andrej1901

- Zadatak Boundary-scan arhitektura

Slike se nalaze na stranicama 165-167.

Opis: u svaki integrirani sklop na svaki ulazni i izlazni priključak stavi se po jedna boundary scan ćelija. Te ćelije omogućavaju da se ono što je došlo iz izlaznih priključaka u ćeliju upiše i da se onda posmakne kroz posmačni registar (shift registar) prema van. U njega se mogu upisivati podaci ili ispisivati, to je serijski read odnosno write. Može i paralelno pratiti što je ušlo preko priključaka, a može se i forsirati što će ući i izaći van na prikljjučak.

Svaka ćelija ima serijski i paralelan ulaz i izlaz i mogu se po potrebi odspojiti.

Možemo puniti lanac, pobuđivati signale ili signale koji su stigli možemo ih zapamtiti i kasnije pročitati to sve pomoću bistabila

Andrej1901

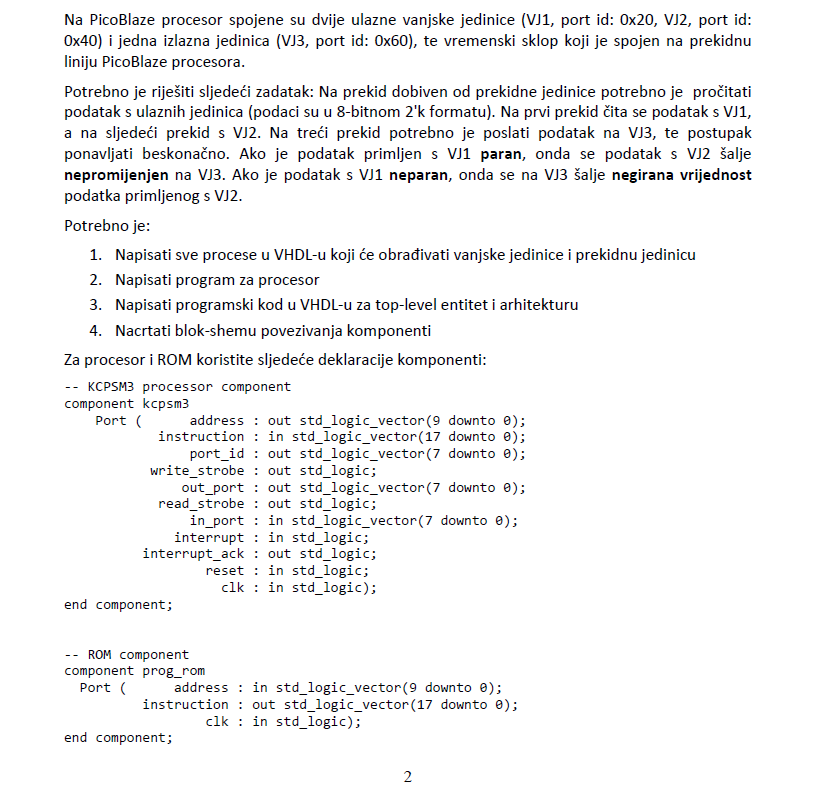

- Zadatak PicoBlaze

Opis: to je 8-bitni procesor, instalacijske memorije su 0.5K, 1K, 2K, 4K. Memorija sadrži program koji izvodi procesor, program je spremljen u Blok memoriju i veličina ovisi o FPGA sklopu i veličini programa.

RISC naredbe veličine 18-bita, sve instrukcije traju 2 takta.

Brzine rada ovise o FPGA sklopu.

Na PicoBlaze moguće je spojiti 256 ulaznih i 256 izlaznih vanjskih jedinica.

Pripada FRISC arhitekturi (ovo provjerit al mislim da je 8-bitna RISC arhitektura al on je naveo FRISC)

Postoje samo dvije zastavice a to su Zero (Z) i Carry ©.

Podržava AND OR XOR, zbrajanje, oduzimanje, pomak i rotaciju, Test i Compare.

Ljudi slobodno i vi koji odgovor objavite nemojte se sramit 😀 svima će puno pomoć bilo kakav odgovor pa makar i djelomicno tocan.

nairobi

- zadatak - pronađeno u starijim materijalima

library IEEE; use IEEE.std_logic_1164.all entity COUNTER is port( brojac: out std_logic_vector (15 downto 0); dodaj: in std_logic_vector (3 downto 0); UP_DOWN: in std_logic; ENABLE: in std_logic; RESET: in std_logic; CLK: in std_logic ); end COUNTER; architecture ARHITEKTURA of COUNTER is variable count := std_logic_vector (15 downto 0); variable ulaz := std_logic_vector (3 downto 0); ulaz := dodaj; begin process(RESET, CLK, ENABLE, UP_DOWN) begin if RESET = ‘1’ then count := ‘0000 0000 0000 0000’; end if; if CLK’event and CLK=’1’ then if ENABLE = ‘1’: if UP_DOWN = ‘1’ then count = count + ulaz; elsif UP_DOWN = ‘0’ then count = count – ulaz; end if; end if; end if; brojac <= count end process; end ARHITEKTURA;

Andrej1901

Kvarcov oscilator, (moglo bi bit)

shema kvarcnog oscilatora str.68, nadomejsna shema str.69, i Piercov oscilator str.71,

opis: Kvarcni oscilator koristi kvarc da bi stabilizirao frekvenciju tj. da odredi frekvenciju oscilatora. Drugi dio ovog oscilatora je digitalni sklop, tj. pojačalo. Pločica kvarca koja je obrađena i na nju se napare dvije pločice metala sa svake strane po jedna elektroda, potom se izvuku dvije žice i stavi u kučište. Kad na tu pločicu dovedemo signal ona počinje titrati zbog piezo-električnog efekta, moguće je pogoditi rezonantnu frekvenciju koja je dalje bitna za oscilator. Postoje serijska i paralelna rezonantna frekcencija i jako su blizu jedna drugoj. Da bi iskoristili oscilator potrebno je dodati digitalni sklop. Najbolje pogledati shemu Piercovog oscilatora, serijska rezonanca predstavlja kratki spoj dok paralellna predstavlja prazan hod, Piercov radi negdje između te dvije frekvencije, glavna komponenta je kvarcni oscilator i invertirajuče pojačalo.

Joseph

Ovo su moja rješenja dijela ispita koji se odnosi na 4 ciklus.

U zadnjem ne znam ovaj vhdl dio za top lvl entitet ali mislim profesoru poslati mail pa javim ako mi odgovori.

Ako sam u nećemu pogriješio ili samo se nevidi pročitati pitajte.

milic

Joseph top level bi valjda trebala bit datoteka u kojoj povezes sve vanjske jedinice, procesor i rom

Joseph

Ovo je moj kratki sažetak 4. cjeline.

Mislim da možete zanemarit veći dio ove teorije mislim da je samo PicoBlaze bitan možda eventualno PROM,

Ali ako netko ima nešto za nadodat ili je našao koju grešku slobodno nek se javi.

Stavio bi kao pdf ali neda forum.

verratti

Trava Istina da, onda bi mogli definirati brojac izvan funkcije kao int brojac = 0; ?

Vuk99

Rom Jova (Željezo/bakar) ja sam mislio definirat neki static int izvan tih funkcija

Joseph

Riješio sam dio s 3. cijelinom opet ispričavam se na rukopisu i nasam se da slike nisu previše mutne.

Ako je nešto krivo samo vičite.

Za ovaj drugi uopće nisam siguran jeli točan, ali ovo je moj pokušaj.

Filozof

- Zadatak - Pitaj Boga jel valja ovo, ali vidim da nitko nije ništa stavio pa ako vidite grešku, javite

//retarget.c

#include <stdio.h> // decl. of FILE, __stdin, __stdout

#include <rt_sys.h> // declaration of _sys_exit, etc.

// to warn in all semihosting calls are not redefined

__asm(".global __use_no_semihosting");

int fputc(int c, FILE *f) {

(void)f; // suppress warning for unused parameter

GPIOD -> IDR &= 0x00000000;

GPIOD -> IDR |= (c << 8); // GPIO 8-15

return(c);

}

int fgetc(FILE *f) {

volatile uint32_t c;

(void)f; // suppress warning for unused parameter

c = GPIOD -> (IDR & 0x000000FF); // GPIO 0-7

return( c );

}

int ferror(FILE *f) {

(void)f;

return 0;

}

__attribute__((noreturn)) void _sys_exit(int return_code){

(void)return_code;

while(1);

}

// main

#include <stm32f407xx.h>

#include <stdio.h>

extern void init_GPIOD(void);

int main (void) {

init_GPIOD(); // Inicijalizacija GPIOD

volatile uint32_t c;

while (1) {

scanf("%d",c);

if (c%2 == 0){

c++;

}

printf ("c");

}}

Joseph

Filozof Ja sam to riješio pomoću onih sys funkcija (pogledaj objavu gore druga slika).

Ja sam to redio preko sysa zbog labosa jer tamo to koristili.

Iskreno nz jeli krivo ili točno ali tvoje mi se više sviđa jer je kraće.

Joseph

Filozof Ne znam jeli se isplati sad poslat mail profesoru u nadi da nam odgovori.

Bobinator

Filozof za fputc, nisam siguran sto si radio sa IDR, jer je on samo za read, jesi mislio mozda na ODR? reset izlaza i onda postavljanje c shiftanog?

nairobi

Joseph pomocu sys funkcija se radi ako se radi o neposrednom koristenju semihost poziva

milic

Joseph jel treba jos nesto dodatno za scanf osim _sys_read() redefinirat ak idemo neposredno

Joseph

light_grandma aha da izgleda da nisam pročitao zadatak dobro onda je ovo od Filozofa dobro.